Introduction to VHDL

Contents

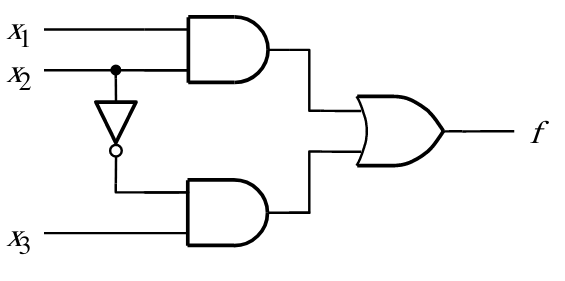

Originally circuit diagrams were used to describe the implementation of the circuit. However as more and more components are added - it becomes hard to maintain and add.

Hardware Description Languages (HDLs) serve as a way to literally describe the circuit (rather than what is executed on a processor)

- VHDL - Very-High-Speed-Integrated-Circuit HDL

- Verilog

VHDL

Note: Syntax is case-insensitive

Entity Declaration

A VHDL entity declaration describes the interface of the circuit.

| |

Architecture

The architecture of a VHDL design unit describes the behaviour/structure of the circuit.

| |

- Simple signal assignment statements are examples of concurrent assignment statements - as they are all evaluated at the same time.

- The order therefore does not matter

STD_LOGIC

The std_logic package defines legal values

- 0

- 1

- Z - High Impedance

- - - Don't care

- U - Uninitialised

- X - Unknown

- W - Weak

- L - Weak tending to 0

- H - Weak tending to H

To use the library, we need to include the following two lines in the code

| |